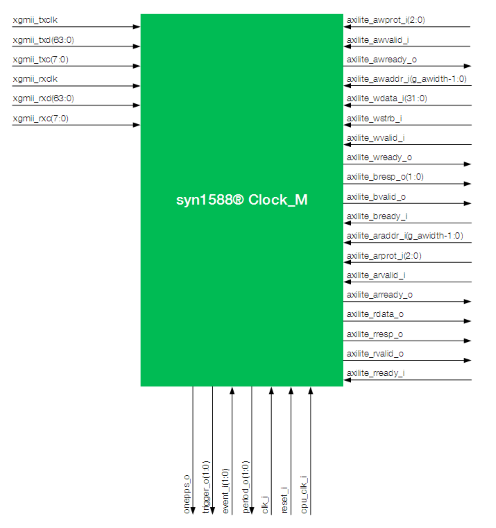

syn1588® Clock_M

Product Description

The syn1588® Clock_M IP core family provides highly accurate IEEE1588 compliant clock synchronization functions. The syn1588® Clock_M IP cores are suited for direct integration to an Ethernet MAC. Either one or up to four network interfaces can be connected. A large variety of network line speeds are supported. There is an AXI4 Lite CPU interface for communication with the host processor executing the PTP Stack.

syn1588® Clock_MIP 코어 제품군은 high-accuracy PTP node를 구현하는 데 필요한 모든 기능을 제공합니다. 기능이 풍부한 아키텍처를 통해 PTP slave 및 PTP 마스터 node를 생성할 수 있습니다. 정교한 하드웨어 시계 아키텍처를 통해 세밀한 시계 servo 제어가 가능합니다. 게시된 모든 IEEE 1588 표준이 지원됩니다.

일반적인 애플리케이션 예로는 syn1588® PCIe NIC가 있습니다. 이 표준 PCIe 이더넷 네트워크 인터페이스 카드는 syn1588® Clock_MIP 코어와 이더넷 MAC 및 PCIe 인터페이스를 포함하는 단일 FPGA로 구성됩니다

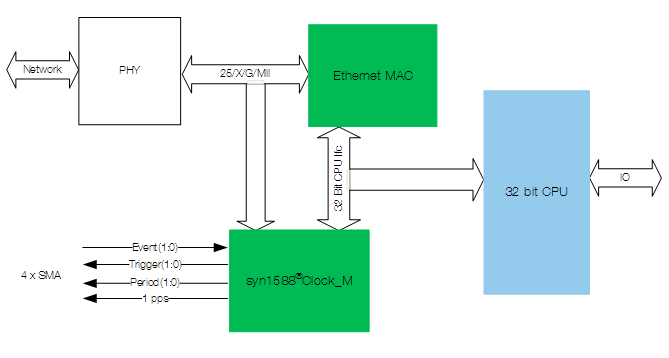

The following figure shows a typical application scenario. Every member of the syn1588® Clock_M IP core family is made up of the following four major function blocks:

· CPU interface

· High-precision hardware clock with clock control

· Network timestamping unit for the selected network speed/type

· Signal Generation

The syn1588® Clock_M IP core is typically accompanied by an Ethernet MAC, an (eventually external) Ethernet PHY and a CPU.

· fully synchronous to the system clock

· all registers of the core operate with the rising clock edge

· well commented, structured VHDL source code

· medium footprink and medium I/O count

· AXI4 Lite type slave interface for clock control using independent CPU clock domain

· C/XL/25/X/G/MII network interface for IEEE1588 network packet timerstamping

· optional user-programmable time stamper unit

· Oregano System's patented on-the-fly-time-stasmping (1-step operation)

· 100/1000 Mbit/s link spped support

· 10 Gbit/s link spped support

· 25 Gbit/s link speed support

· 40 Gbit/s link speed support (4x10 Gbit)

· 100 Gbit/s link speed support (4x25 Gbit)

· two timestamp input signals (EVENT function).

One EVENT input offers FIFO to capture dense events. This can be used to synchronize to an external GPS-based time source via 1 PPS signal.

Minimum pulse width is 3 x syn1588® clcok period.

· Generation of two one-time events (TRIGGER function). One TRIGGER output offers a FIFO to generate dense and precise events.

TRIGGERs may be used to start the PERIOD function to allow a precise absolute phase definition in the whole PTP network

· two PERIOD outputs allowing generation of periodical signals (clock) in a frequency range from mHZ with a resolution of 2-45 ns

· one 1pulse per second (PPS) output

· generation of digitsal IRIG-B output stream (DCLS mode IRIG-B0000)

· decoding of digital IRIG-B input stream (DCLS mode IRIG-B000)

· generation of inperrupts upon external inrernal events

· pipelined adder bssed clock for best

· separate receive and transmut timestamp FIFOs

· clock time format compatible to the IEEE1588 standard

· suited for FPGA as well as ASIC implementations

· optional SMPTE 2059 compatible signal genetation